РАЗРАБОТКА

КОНТРОЛЛЕРОВ ВСТРАИВАЕМЫХ СИСТЕМ НА ОСНОВЕ ПЛИС С ИСПОЛЬЗОВАНИЕМ Matlab

(Simulink)

Кали Маржан КАХАРМАНКЫЗЫ

магистрант кафедры

радиотехники электроники и телекоммуникации

Евразийского

Национального Университета имени Л.Н.Гумилева

Мухитден Улыкбек Сагиденулы

магистрант Казахского

Агротехнического Университета имени С.Сейфуллина

Встраиваемые системы управления используется

в различных приложениях, таких как бытовая электроника, медицинское

оборудование, робототехника, автомобильная продукция и промышленные процессы. Для

реализации встраиваемых систем управления обычно используют микропроцессоры,

микроконтроллеры или цифровые сигнальные процессоры (DSP).

Алгоритмы управления реализуются как

программные программы, которые выполняются на аппаратном процессоре с

фиксированной архитектурой. К процессору (микроконтроллеру) подключены различные

периферийные устройства, такие как запоминающие устройства, аналого-цифровые

преобразователи и другие устройства ввода/вывода. При этом альтернативно, программируемые

логические интегральные схемы (ПЛИС)становятся популярными в качестве платформы

для реализации встраиваемых систем, алгоритмы управления которых реализуются

путем программирования реконфигурируемых аппаратных логических ресурсов

устройства [1].

В настоящее время ПЛИС обладают всеми характеристиками,

которые делают их пригодными для аппаратных реализаций алгоритмов и систем, за

счет вычислительного параллелизма, реконфигурируемой настройки и быстрогопрототипирования.Также

развитие технологий производства делает привлекательным использование ПЛИС,

т.к. их стоимость приближается к стоимости микроконтроллеров и DSP. Более того,

реализация на основе FPGA может снизить общую стоимость системы, так как многие

компоненты конструкции могут быть реализованы как чип с системой на

микропроцессоре [2, 3]. В некоторых случаях реализации на основе FPGA могут

давать более высокие уровни производительности для проектирования по сравнению

с другими реализациями. В таких случаях ПЛИСмогут быть единственным выбором для

реализации, потому что микроконтроллеры и ПЛИСне будут соответствовать

требованиям к производительности, а интегральные схемы для специализированных

интегральных схем (ASIC) могут иметь слишком высокие затраты на разработку.

Одним из отличий при проектировании систем на

ПЛИС является использование для разработки языка описания аппаратных средств,

таких как Verilog или VHDL. Однако языки описания аппаратных средств описывают

взаимодействия на низкоуровневом уровне (битов, регистров и логических

функций), в отличие от высокоуровневых языков микроконтроллеров, где

рассматриваются сигналы, переменные и математические функций. Тем не менее, для

устранения этого разрыва имеются инструменты для разработки ПЛИС на высоком

уровне. Некоторые из этих инструментов основаны на существующих средах

разработки, таких как Matlab/Simulink или LabVIEW

[4, 5].

В этой статье рассматривается инструментDSP

Builder, разработанный для работы в Simulink, изучается как инструмент

разработки контроллеров на основе FPGA. DSP Builder позволяет использовать

привычную и удобную среду разработки Simulink для разработки для описания ПЛИС.

Таким образом, разрыв между инструментами, используемыми инженерами и средами

разработки ПЛИС, сужается. Следовательно, платформы ПЛИСмогут использоваться

для построения контроллеров встраиваемых систем наряду с микроконтроллерами и

DSP.

Возможности DSP Builder для разработки

контроллеров расширены за счет разработки библиотеки пользовательского

управления в Simulink. В пользовательской библиотеке содержатся блоки,

основанные на DSP Builder, которые могут использоваться для быстрой разработки

контроллеров на основе ПЛИС. Для разработки с использованием DSP Builder

требуются как программные пакеты Simulink, так и Quartus II.

DSP Builder предоставляет специальные

библиотеки блоков для использования в Simulink, которые непосредственно

синтезируются в аппаратную логику для устройств ПЛИС. ПЛИС-реализуемые

алгоритмы и системы могут быть разработаны путем простого перетаскивания блоков

библиотеки DSP Builder в файл модели Simulink и установления желаемых связей

между ними. Каждый блок DSP Builder имеет прямое представление HDL (в Verilog

HDL или VHDL) функции, которую он выполняет, то есть блоки инкапсулируют модули

HDL. Специальный блок под названием SignalCompiler при вызове считывает файл

модели Simulink и переводит каждый из блоков DSP Builder и их взаимосвязей в

соответствующие представления HDL. Каждый из блоков DSP Builder может иметь

свои параметры, определенные через диалоговые окна в Simulink, и эти варианты

параметров распространяются в их представлениях HDL. Наконец, SignalCompiler

объединяет весь проект в один объект высшего уровня HDL, который может

обрабатываться через этапы проектирования ПЛИС, используя Quartus II. Объект

HDL будет функционально эквивалентен системе в файле модели Simulink при ее

выполнении на ПЛИС [6].

Библиотечные блоки DSP Builder также

поставляются с точными и точными по времени имитационными моделями, которые

могут использоваться численными решателями Simulink для выполнения

моделирования в среде Simulink. Кроме того, для целей моделирования только

существующие блоки Simulink (такие как источники ввода) могут быть связаны с

блоками DSP Builder для выполнения более сильных имитаций с участием подсистем

реального мира, которые взаимодействуют с FPGA. Это имеет очевидное

преимущество для встроенной системы управления проектами в том смысле, что

ожидаемое поведение контроллера на базе DSP Builder можно моделировать с

помощью модели на базе Simulink. Таким образом, реакцию контроллера можно

удобно моделировать и анализировать. Это моделирование использует численные

решатели Simulink и отличается от моделирования на уровне HDL с использованием

симуляторов RTL. Тем не менее, из-за точности битов и циклов поведение дизайна

на основе DSP Builder в Simulink будет соответствовать поведению

сгенерированной системы HDL, когда она выполняется на ПЛИС. Таким образом,

проект можно моделировать, анализировать и затем модифицировать на более

высоком уровне абстракции, чем на уровне HDL. Этот процесс устраняет

необходимость прохождения потока проектирования ПЛИСна каждой итерации проекта,

что приводит к сокращению времени разработки.

Существует пять основных типов блоков,

предоставляемых DSP Builder: арифметические блоки, логические операции и блоки

управления потоком (в библиотеке Gate&Control), входные, выходные порты и

блоки управления шиной (в библиотеке IO &Bus), область Clock и временные

блоки выборки и блоки для хранения сигналов и данных (в библиотеке хранения).

Учитывая математическое описание контроллера (в частности, в канонической

форме), контроллер может быть реализован с использованием трех операторов:

множителей, сумматоров и элементов задержки. Поэтому любой контроллер может

быть легко реализован в DSP Builder и реализован как аппаратное обеспечение на ПЛИС.

Хотя блоков множителя, сумматора и задержки может быть достаточно, разработка с

использованием этих блоков может быть утомительной и отнимающей много времени.

Библиотечные блоки DSP Builder предлагают

базовые функции, которые могут быть использованы для разработки

пользовательских блоков для выполнения более сложных функций. Они могут быть

использованы для разработки заказной библиотеки строительных блоков системы

управления для быстрой реализации встроенных контроллеров на основе ПЛИС. Например,

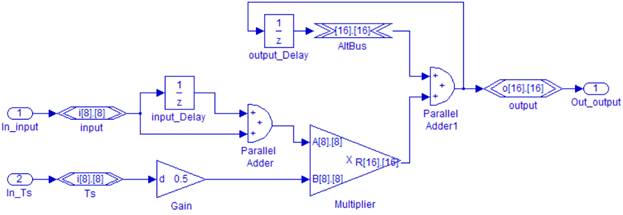

на рисунке 1 приведена реализация специализированного компонента библиотеки

управленияIntegrator, где блок «Параллельный сумматор» добавляет вход e(k) к предыдущему вводу e(k-1), который создается из блока

«input_Delay», и затем умножается на Ts/2

(= T/2). Выход блока «Множитель» добавляется к предыдущему значению вывода,

которое сохраняется и становится доступным из блока «output_Delay». Поскольку

текущий выходной сигнал возвращается обратно в блок «output_Delay», ширина бита

сигнала в блоке является неопределенной, и поэтому ее необходимо явно

определить. Это может быть достигнуто блоком «AltBus». Ширина бита для «AltBus»

автоматически выбирается такой же, как и битовая ширина результата множителя.

Ширина бита для выходного сигнала «output» также выбирается такой же, как и для

результата умножения.

Рисунок 1 – Реализация блока Integratorпользовательского

элемента управления с использованием блоков DSP Builder.

Таким образом в работе рассмотрено

использование инструментария системного уровня DSP Builder для высокоуровневой

разработки контроллеров встраиваемых систем на основе ПЛИС. Возможности

инструмента DSP Builder были расширены за счет разработки блока

пользовательского управленияIntegrator, который в дальнейшем может

использоваться, например, для реализации PID

контроллера.

Литература

1.

Casalino, G., Giorgi,

F., Turetta, A., &Caffaz, A. (2003). Embedded FPGA-based control of a

multifingered robotic hand, IEEE Int. Conf. on Robotics &Auto.m, pp.

2786-2791.

2.

Chan, Y.F., Moallem,

M. & Wang, W. (2007). Design and implementation of modular FPGAbased PID

controllers, IEEE Transactions on Industrial Electronics, 54(4), pp. 1898-

1906.

3.

Jung, S-L., Chang,

M-Y., Jyang, J-Y., Yeh, L-C., &Tzou, Y-Y. (1999). Design and implementation

of an FPGA-based control IC for AC-voltage regulation, IEEE Transactions on

Power Electronics, 14(3), pp. 522-532.

4.

Koutroulis, E.,

Dollas, A., &Kalaitzakis, K. (2006). High-frequency pulse width modulation

implementation using FPGA and CPLD ICs,” Journal of Systems Architecture,

52(6), pp. 332-344.

5.

Oh, S-N., Kim, K-I.,

& Lim, S. (2003). Motion control of biped robots using a single-chip

drive", IEEE Int.l Conf. on Robotics &Autom., pp. 2461-2465.

6.

Tessier, R., &

Burleson, W. (2001). Reconfigurable computing for digital signal processing: A

Survey, The Journal of VLSI Signal Processing, 28(1), pp. 7-27.

Сведения

об авторе:

1. Кали Маржан Кахарманкызы.

2. Магистрант.

3.

ЕНУ имени Л.Н.Гумилева.

4.

kali.marzhan@mail.ru

5.

Почтовый адрес: 010000, г.Астана,

ул.188 (новая Косшыгулова), д.11,

кв.289.

6.

8-(775)-295-07-37.

7.

Рубрика «Технические науки»

8.

Количество журналов: 1 (один).

Сведения

об соавторе:

1. Мухитден Улыкбек Сагиденулы.

2. Магистрант.

3.

КазАТУ имени С.Сейфуллина.

4.

kuandykmk@mail.ru

5.

Почтовый адрес: 010000, г.Астана,

ул.188 (новая Косшыгулова), д.11,

кв.289.

6.

8-(775)-299-96-05.

7.

Рубрика «Технические науки»

8.

Количество журналов: 1 (один).