*112762*

Технические науки/6. Электротехника и радиоэлектроника

Капитанов

А.А., к.т.н. Остапенков П.С.

«Национальный

исследовательский университет «МЭИ» », Россия

ПРАКТИЧЕСКИЕ ОСОБЕННОСТИ ИСПОЛЬЗОВАНИЯ ПЛИС ДЛЯ ЦИФРОВОЙ ОБРАБОТКИ

СИГНАЛОВ

В докладе рассматриваются вопросы практического использования программируемых логических интегральных схемах (ПЛИС) для реализации элементов трактов цифровой обработки сигналов радиоприемных устройств. Основное внимание в докладе уделяется реализации на языке VHDL сложного узла тракта обработки сигналов цифрового приемника, выполняющего быстрое преобразования Фурье (БПФ). Реализация модулей цифровой обработки сигналов поводилась на ПЛИС семейства Virtex 5 с использованием систем автоматизированного проектирования (САПР) “Active-HDL” фирмы «Aldec» и “ISE Design Suite” фирмы «Xilinx».

В настоящее время в области разработки цифровых схем все более широкое использование находят ПЛИС [1,2]. ПЛИС – это своеобразный электронный компонент, используемый для создания сложных, многофункциональных устройств цифровой обработки сигналов. В отличие от большинства обычных цифровых микросхем, логика работы ПЛИС не определяется при изготовлении, а задаётся посредством программирования, что является существенным достоинством ПЛИС, позволяющим создавать требуемую структуру цифрового устройства, увеличить скорость разработки и отладки [3].

Для моделирования и программирования ПЛИС существует большое количество различных САПР. В настоящем докладе рассматриваются вопросы, связанные с использованием САПР “Active-HDL” фирмы «Aldec» и “ISE Design Suite” фирмы «XilinX».

Преимущество ПЛИС по сравнению с микроконтроллерами, процессорами ЦОС (DSP) заключается в выигрыше в скорости вычисления преобразования и гибкой архитектуре, позволяющей распараллеливать различные процессы. Гибкость конфигурирования и высокое быстродействие ПЛИС, большие объемы логических вентилей, ячеек памяти, наличие модулей цифровой обработки сигналов (DSP) и банков цифровых фильтров, а также встроенных микропроцессорных ядер и буферов поддержки современных интерфейсов существенно расширяют возможности разработчиков [2]. Поэтому область применения ПЛИС широка: это телекоммуникации и сетевые технологии, аудио- и видео-обработка, промышленное оборудование, измерительная и медицинская техника, специальная аппаратура и т.д.

Алгоритмы БПФ являются одними из базовых

инструментом

анализа в современной цифровой обработке сигналов (ЦОС) [4-6], поэтому в

представленном докладе им будет посвящено основное внимание.

В настоящее время существует большое количество реализаций алгоритмов БПФ на контроллерах и процессорах, но следует отметить, что реализации алгоритмов БПФ на ПЛИС позволяют создать наиболее оптимальные структурные решения с точки зрения максимальной производительности для современного технологического уровня интегральных схем [3].

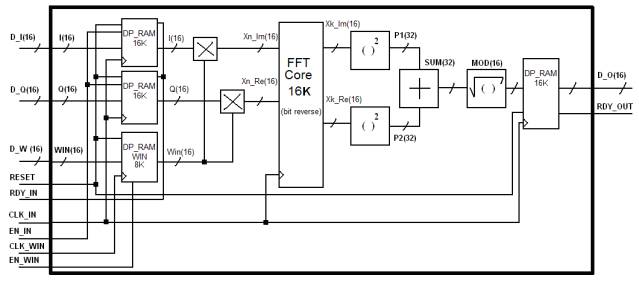

На рис. 1. представлена структурная схема, описывающая реализацию узла БПФ с фиксированной точкой на ПЛИС XC5VLX50T семейства Virtex 5 фиры «Xilinx».

Рис. 1. Структурная схема узла БПФ.

Схема содержит ряд вложенных блоков, при формировании которых, в числе прочих использовалось приложение ”Core Generator” пакета “ISE Design Suite” фирмы “Xilinx” [7]. Ниже приводится назначение элементов схемы:

- FFT Core 16К – IP-ядро БПФ, размер преобразования равен 16384 (16К) точек;

- DP_RAM 16К – двухпортовые входные и выходные блоки оперативного запоминающего устройства (ОЗУ);

- DP_RAM 8К – двухпортовое ОЗУ для загрузки оконной функции D_W,

- два блока умножения входных данных на функцию, представленную массивом коэффициентов;

- блоки возведения в квадрат для реальной и мнимой частей спектра;

- общий сумматор;

- блок взятия квадратного корня.

Входные и выходные данные представлены 16-разрядными двоичными числами. Входные данные пачками размером 16K непрерывно в прямой форме поступают на блоки DP_RAM двухпортовых ОЗУ. Глубина ОЗУ задается в соответствии с максимальным объемом пакета и составляет 16К. Входная частота равна тактовой частоте ПЛИС: CLK_IN - 100 МГц. Разрядность блоков DP_RAM выбирается равной разрядности обрабатываемых данных (16 бит).

В двухпортовый блок ОЗУ DP_RAM WIN размером 8К однократно загружается половина последовательности коэффициентов с порта DATA_WIN с частотой CLK_WIN – 50 МГц. Поскольку последовательность входных данных симметрична относительно центрального отсчета, то можно использовать простой прием, особенность которого состоит в том, что после загрузки данных в ОЗУ, данные выгружаются сначала в прямом порядке (по увеличению индекса адреса ОЗУ), а затем в обратном (по убыванию индекса адреса ОЗУ). В результате на выходе блока WIN образуется симметричная последовательность отсчетов, что позволяет использовать ОЗУ меньшего размера в силу симметрии оконной функции. Частота CLK_WIN используется для синхронизации перемножения входных данных с массивом коэффициентов оконной функции и составляет половину тактовой частоты CLK_IN. Сигнал EN_WIN разрешает синхронную запись коэффициентов в блок WIN по положительному перепаду тактового сигнала CLK_WIN.

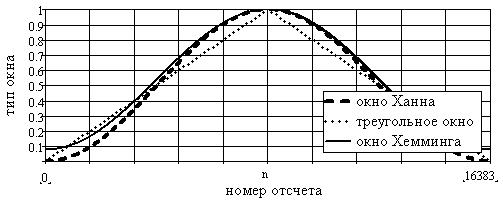

В процессе разработки стояла задача обоснования выбора оконной функции в соответствии с требованиями технического задания. В докладе рассмотрены следующие виды оконных функций: нормированное «треугольное окно», «окно Ханна», «окно Хемминга».

«Треугольное окно» обладает достаточно большим уровнем боковых лепестков (УБЛ) частотной характеристики, порядка -26дБ. Функция нормированного «треугольного окна» описывается выражением (1):

, (1)

, (1)

где n – номер отсчета, N – ширина окна и длина последовательности.

Уровень боковых лепестков частотной характеристики для «окна Ханна» составляет -31.5 дБ и определяется выражением (2):

. (2)

. (2)

Из представленных выше вариантов функций «окно Хемминга» обладает лучшим УБЛ -42дБ и описывается выражением (3):

. (3)

. (3)

Вид рассмотренных «окон» приведен на рис. 2.

Рис. 2. Вид оконных

функций.

Тот или иной выбор оконной функции определяется требованиями, выдвигаемыми к характеристикам модуля БПФ и возможностями ПЛИС. На начальном этапе создания модуля БПФ наиболее удобно использовать оконную функцию «треугольного окна» как самую простую для программной реализации, для её формирования может быть использован обычный двоичный счетчик. Более сложные для реализации оконные функции можно включать в проект позднее на этапе функционального моделирования при необходимости соответствия более строгим техническим требованиям, выдвигаемым к блоку БПФ. Для хранения значений оконной функции используется блок ОЗУ DP_RAM WIN.

После записи и выгрузки данных из входных ОЗУ, данные поступают на блоки перемножителей, где происходит корректировка входных данных в соответствии с коэффициентами оконной функции, хранящейся в ОЗУ DP_RAM WIN. После этого данные в прямой форме, записываются в ядро БПФ, и в блоке FFT Core 16К происходит вычисление БПФ по алгоритму Radix-2 (по основанию 2 с прореживанием по времени и пакетным режимом ввода-вывода). С выхода блока FFT Core 16К данные поступают на блоки схемы, которые выполняют вычисление модуля комплексного числа. Для этой цели используются два блока возведения в квадрат для реальной и мнимой частей, сумматор и устройство взятия квадратного корня. Таким образом, вычисляется модуль комплексного числа, то есть определяется спектр входного сигнала. Следует учесть, что блок вычисления модуля комплексного числа может быть упрощен, а результат операции определяется как сумма модулей вещественной и мнимой частей сразу после звена БПФ.

Данные на выходе блока БПФ упорядочены в бит-реверсной последовательности, что позволяет существенно уменьшить время преобразования в блоке БПФ за счет выполнения перестановки в выходном ОЗУ DP_RAM 16K.

В числе управляющих сигналов в схеме присутствует сигнал глобального сброса – RESET, который обнуляет все внутренние шины, ОЗУ, ядро БПФ. Сигнал готовности входных данных RDY_IN принимает состояние логической «1» при полной загрузке данных в узел БПФ. Сигнал RDY_OUT сигнализирует о готовности выходных данных и принимает состояние логической «1» по окончании выгрузки данных. Сигнал разрешения EN_IN разрешает синхронную запись данных во входное ОЗУ по фронту тактовой частоты.

Таким образом, в процессе выполнения был

решен ряд следующих задач:

–

проведен расчет и

моделирование в пакетах "Mathcad" и "Matlab” модуля БПФ, оконных

функций, цифровых КИХ-фильтров с заданными параметрами для тракта обработки

сигналов цифрового приемника;

–

разработаны модули

прикладных программ для ПЛИС семейства Virtex 5 (XC5VLX50T) на языке VHDL, реализующие узел БПФ с

размерностью 16384 точек (алгоритм – по основанию 2 с прореживанием времени с

фиксированной точкой), цифровые КИХ - фильтры с требуемыми параметрами;

–

проверка

работоспособности узлов прикладной программы для ПЛИС осуществлялась на модуле

обработки сигналов ”Ambpex5” фирмы “Инструментальные

системы”.

В докладе показана эффективность использования ПЛИС для реализации алгоритмов цифровой обработки сигналов. Использование ПЛИС для реализации элементов цифровой части трактов обработки сигналов радиоприемных устройств позволяет уменьшить количество интегральных схем, используемых для реализации устройства, сократить энергопотребление, упростить этапы проектирования и конфигурирования устройства.

Предложенные в докладе подходы по реализации модулей

БПФ и цифровых фильтров на базе ПЛИС могут быть использованы при реализации

трактов обработки сигналов быстродействующих радиоприемных устройств.

Библиографический

список

[1] Айчифер Эм., Джервис Б.

Цифровая обработка сигналов: практический подход. 2-ое издание. Пер. с англ. -

М.: Издательский дом “Вильямс”, 2004.

[2] Перекрест А.А. «Преимущества использования сопроцессоров на базе ПЛИС FPGA в системах цифровой

обработки сигналов», 4с., Электроника: Наука, Технология, Бизнес № 6, стр.

110-113, 2006.

[3] S. Sukhsawas and K. Benkrid, “A high-level

implementation of a high performance pipeline FFT on Virtex-E FPGAs,” IEEE

Computer Society Annual Symposium on VLSI, pp. 229-232, 2004.

[4] P. Duhamel and M. Vetterli, “Fast Fourier

transforms: a tutorial review and a state of the art,” Signal Processing, vol.

19, pp. 259–299, Apr. 1990.

[5] M. Frigo and S.

G. Johnson, “The design and implementation of FFTW3” Proc. IEEE, vol. 93, no.

2, pp. 216–231, 2005.

[6] Lin, H.C.; Lee, C.S. Enhanced FFT-based parametric algorithm for simultaneous multiple harmonics

analysis. Generation, Transmission and Distribution, IEEE Proc.

Vol. 148 , no. 3, pp. 209-214, 2001.

[7] LogiCORE IP

Fast Fourier Transform, v7.1 DS260, Xilinx Inc., 2011.