современные информационные

технологи/компьютерная инженерия.

Рябцев В.Г., Люта М.В., Комарницкий А.В., Гучок

В.В., Скрипка Я.С.

Киевский национальный

университет технологий и дизайна, КНУТД

Особенности встроенного

самотестирования микросхем памяти систем на кристалле

Современное тестирование электроники исторически

начинается с введением коммерческого производства интегральных схем (ИС) в

начале 1960-х, и насчитывает более 50 лет использования. Интегральная схема

была разработана в 1958 году, одновременно в Texas Instruments (TI) и Fairchild

Semiconductor. Сегодня полупроводники лежат в основе многих текущих достижений

в отрасли электроники. Внедрение новых технологий, особенно нанометровой

технологии, позволило полупроводниковой промышленности идти в ногу с запросами

потребителей. Затраты на производство ИС могут в настоящее время составлять 40%

от общей стоимости продукта. Кроме того, качество продукции и ее

востребованность могут значительно снизиться, если эти чипы не предназначены

для тестирования[3].

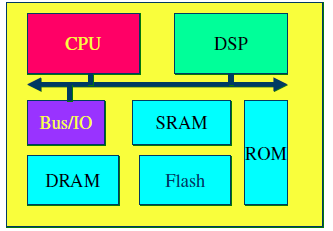

Создание и внедрение системы чипов создает новые

проблемы для исследователей. Число встроенной памяти ядра быстро расширяется, и

следовательно занимает память на системных чипах.

Рисунок 1. Структура ядер систем на

кристалле

Таким образом, выход на чипе памяти определяет

выходы работоспособных чипов. Go / no-go тестирования уже не достаточно для

встроенной памяти в системе на чипе (System-on-Chip,

SOC). Диагностика памяти быстро становится одним из важнейших вопросов,

поскольку доходность производства и

время выхода на объем продукции SOC не стабильна. Применение методики

эффективной диагностики памяти и анализ отказов (FA) позволяет повысить качество

продуктов SOC.

Рассмотрим неисправности моделей памяти и

тестирование алгоритмов. Представим симулятор неисправности памяти, называемый

случайный симулятор доступа к памяти, для ошибки скрининга, которая состоит из

моделирования многочисленных дескрипторов. Моделирование считывает тестовые

воздействия и устанавливает флаги операций для каждой ячейки памяти.

Неисправность покрытия определяется путем проверки неисправности дескрипторов

для определенных условий. Генератор моделирования и случайных алгоритмов будет

представлен, на основе тест-алгоритмов RAMSES

и March. March-тесты считаются наиболее эффективными для обычных моделей оперативной памяти. Их легко создавать и,

как правило, они короткие [2].

С появлением глубоких субмикронных с очень высокой

степенью интеграции (VLSI) технологий, продавцы обращаются к SOC. Потому что

почти все чипы системы содержат некоторые виды встроенной памяти, память

считают одним из наиболее универсальных компонентов. Процент от стоимости встраиваемой памяти на общем рынке

полупроводниковой памяти вырастет до 50% и более в будущем. Так как эта тенденция

широко распространена, тестирование встроенной памяти получает все большее

внимание со стороны промышленности, а также научного сообщества.

Есть много проблем в объединении памяти (DRAM,

флэш-память и т. д.) с логикой. В дополнение к существующим техническим проблемам

для гарантирования производительности, качества и надежности встроенной памяти

ядра, требуются дальнейшие исследования.

В методологии дизайн-для-проверки (Design-For-Test)

должна быть предусмотрена изоляция ядра тестом доступа, который должен быть

включен в себестоимость разработки, но это в свою очередь снижает

производительность и вызывает нежелательные эффекты. Даже если эта методология

являются выполнимой, то тестирование памяти для полной квалификации и

тестирование встроенной DRAM (EDRAM) будет более дорогостоящим, из-за увеличения скорости ввода / вывода и

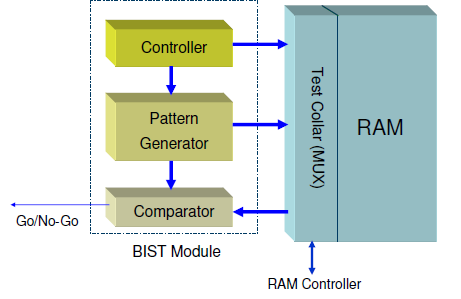

объема данных. Перспективным решением этой дилеммы является использование

технологии BIST (рисунок 2).[1]

Рисунок 2. Типичная архитектура памяти

BIST

С применением BIST требование тестирования EDRAM

может быть сведено к минимуму, а время тестирования памяти может быть уменьшено

в течение всего срока проверки EDRAM. Кроме того, общее время тестирования

может быть уменьшено, поскольку параллельное тестирование в банке памяти выполнять

проще.[2]

Таблица 1. - Экспериментальные результаты

|

ПЗУ размер |

256x8 |

2048x8 |

2048x64 |

4096x32 |

|

BIST счет |

436 |

455 |

930 |

561 |

|

Период времени (ns) |

2.44 |

2.8 |

3.46 |

3.51 |

|

Время

проверки(clockcye) |

267 |

2059 |

2115 |

4131 |

Таким образом, BIST будет, широко применяться

для тестирования EDRAM. Еще одно

преимущество BIST состоит в том, что это хороший подход к защите

интеллектуальной собственности (IP), то есть производитель (EDRAM ядра в данном

случае) должен поставлять только активации BIST и последовательности реагирования

для тестирования и диагностики целей без раскрытия деталей проектирования [3].

Хотя BIST был успешно применен для встроенных

SRAM (ESRAM), его успех во встраиваемых DRAM, флэш-памяти, CAM и т.д., еще

предстоит выяснить. Необходимость внешнего тестирования памяти EDRAM не может

быть проигнорирована, если анализ избыточности и ремонт можно сделать на чипе.

Кроме того, новые виды отказов или сбоев должны быть протестированы и с помощью

March алгоритмов, таких как те, которые используются в схемах ESRAM BIST, но

которые считаются недостаточными.

Существуют другие проблемы. Сочетание

встроенного датчика памяти и BIST логики также является интересной темой.

Следующей задачей является автоматизация проектирования. Еще одной проблемой

является синхронизация квалификации тестирования или переменной памяти от

асинхронной памяти с синхронной BIST логикой.

Таким образом, затронуты важные аспекты

тестирования полупроводниковой памяти, в том числе, тестирование алгоритмов,

моделирования неисправностей, автоматическую генерацию алгоритмов тестирования

и самодиагностики. Архитектура BIST

поддерживает March -тесты и диагностику. Выбрав соответствующий подход,

она также проверяет сроки спецификаций. Подход является гибким, поскольку

дополнительные команды теста (кроме элементов March) могут быть включены с

минимальными затратами. Использование архитектуры BIST является экономически

эффективным, так как испытание занимает минимум времени, расходы на аппаратные средства низкие, и тестовое

покрытие является объёмным. Компилятор BIST для встраиваемой памяти называется мозгом, который может быть

использован для общих SRAM и DRAM ядер, таких как: синхронные SRAM, асинхронные

SRAM, двойной порт SRAM, два порта регистрового файла, ZBT SRAM, EDO DRAM,

SDRAM , DDR DRAM и т.д. Учитывая память спецификации и требования к испытаниям,

мозг генерирует синтезируемый (RTL) код замыкания для BIST в Verilog, а также

активацию его последовательностей, испытательный стенд, и синтез сценариев. BIST

влияет на скорость тестирования и диагностики оперативной памяти тестируемого,

а March-тесты являются программируемыми. Такой инструмент может быть

использован для широкого спектра оперативной памяти, архитектур и конфигураций.

Кроме того, BIST-схемы могут быть общими для нескольких видов памяти, чтобы

снизить общие накладные области. Поэтому использование BIST очень важно для

проектирования SOC.

Выводы

Сегодня почти все производители внедрили в память

элемент встроенного самотестирования (BIST). К сожалению, популярность

самостоятельного ремонта (BISR) встроенной

оперативной памяти еще не общепринята. Тестирование по-прежнему остается большой

проблемой для гигагерцовой последовательности протоколов ввода/вывода и схем с аналоговыми

смешанными сигналами (AMS). В ближайшей перспективе использование памяти BIST также должно быть распространено на более

реалистичные типы ошибок, такие как задержка неисправностей в BIST и выявление неисправностей

в ячейках памяти. Неисправности, вызванные изменением параметров, должны быть смоделированы

и протестированы. Интеграция методов SOC и испытания (например, повторный тест)

на уровне кристалла по-прежнему остаются

проблемой, и требуют поиска эффективных решений.

В долгосрочной перспективе, к 2018 году, по

данным СПУ [SIA 2004], 90% кремния будет со встроенной самодиагностикой, так

что усилия должны быть направлены на встроенные программные системы

самотестирования, использующие встроенные программируемые ресурсы. Для последующего

развития SOC будут крайне необходимы новые DFT / BIST методы

для программируемых логических матриц (FPGA) тестирования, микроэлектромеханические

системы (MEMS) тестирования, и наличие высокоскоростного последовательного

интерфейса, все это подлежит дальнейшему исследованию со стороны научного

сообщества. Наконец, схемы должны сосуществовать с дефектами в области нанотехнологий,

отказоустойчивость и онлайн-тестирование должны быть встроены в схемы, особенно

для логических сбоев. Таким образом, промышленность должна справиться с

огромным спектром проблем, начиная от тест-уровня синтеза шума интерфейса и до

рассеивания мощности.

Литература

1. C.-W. Wu, Testing embedded memories: is BIST the

ultimate solution?, in

Proc. Asian Test Symp.,

November 1998, pp. 516-517.

2. C.-T. Huang, J.-R. Huang, C.-F. Wu, C.-W. Wu, and

T.-Y. Chang, A programmable BIST core for embedded DRAM, IEEE Des. Test Comput., 16(1), 59-70, 1999.

3. [Prince 1991] B. Prince,

Semiconductor Memories: A Handbook of Design, Manufacture and Application, 2nd ed., John Wiley & Sons, Chichester, 1991.