Современные информационные технологии/1.

Компьютерная инженерия

Д-р техн. наук И.И. Левин, канд. техн.

наук В.А. Гудков,

канд. техн. наук

А.А. Гуленок

НИИ многопроцессорных вычислительных систем имени

академика

А.В. Каляева Южного федерального университета, г.

Таганрог, Россия

Канд. техн. наук А.И. Дордопуло,

канд. техн. наук В.Б. Коваленко

Южный научный центр РАН, г.

Ростов-на-Дону, Россия

Программирование

реконфигурируемых вычислительных систем с помощью софт-архитектур*

Эффективное решение

вычислительно трудоемких задач в различных областях науки и техники возможно с

использованием реконфигурируемых вычислительных систем (РВС), обладающих

высокими реальной и удельной производительностью при решении задач, высокой

энергоэффективностью и др. Различные отечественные и зарубежные компании

создают как отдельные ускорители с одним-двумя кристаллами программируемых

логических интегральных схем (ПЛИС), так и целые вычислительные комплексы.

Такие фирмы как Nallatech [2] и Pico Computing

[3] выпускают ряд ускорителей и несущих плат с небольшим числом (до четырёх)

кристаллов ПЛИС, которые используются в создании серверов и гибридных

кластерных систем фирмами HP и IBM. Компании Convey

[4] и Maxeler Technologies

[5] создают гибридные суперкомпьютеры на основе собственных гетерогенных

кластерных узлов, каждый из которых может содержать от 1 до 4 кристаллов ПЛИС и

несколько универсальных процессоров. Похожее решение используется и компанией SRC [6], которая выпускает узлы, названные MAP processor,

для стойки (MAPstation) форм-фактором 1U, 2U и 4U. MAPstation 1U содержит один MAP processor. MAPstation 2U содержит до трёх MAP processor. MAPstation

4U может содержать до 10 различных модулей – MAP processor, модуль с

универсальным микропроцессором или модуль памяти. Отметим, что наиболее

рациональным способом построения именно вычислительной системы на основе ПЛИС

является использование в качестве основного вычислительного элемента множество

кристаллов ПЛИС, объединенных в единое вычислительное поле высокоскоростными

каналами передачи данных, что позволяет получить мощный вычислительный ресурс,

достаточный для эффективного решения задачи.

В НИИ многопроцессорных

вычислительных систем имени академика А.В. Каляева Южного федерального

университета (НИИ МВС ЮФУ, г. Таганрог) разрабатываются суперкомпьютеры с

возможностью объединения нескольких печатных плат в единый вычислительный

контур, при этом основным вычислительным ресурсом системы являются кристаллы

ПЛИС. Методы разработки и создания таких систем успешно развиваются в НИИ МВС

ЮФУ. Концепция построения РВС [7] позволила создать целый ряд

высокопроизводительных систем различных архитектур и конфигураций, выпускаемых

серийно и предназначенных для решения вычислительно трудоемких задач различных

предметных областей.

Для всех вычислительных

модулей НИИ МВС ЮФУ сохраняется преемственность принципов программирования

[7-10]: программирование всех рассмотренных вычислительных модулей

осуществляется с помощью единого комплекса системного программного обеспечения,

поддерживающего структурно-процедурные методы организации вычислений и

определяющего не только организацию параллельных процессов и потоков данных, но

и структуру вычислительной системы в поле логических ячеек ПЛИС.

Большинство существующих

коммерческих систем проектирования (Xilinx ISE, Altium Designer и другие)

обеспечивает в рамках одного проекта работу только с одним кристаллом ПЛИС.

Поэтому при разработке конфигурации для нескольких ПЛИС инженеру-схемотехнику

приходится самому распределять элементы вычислительной структуры алгоритма

решаемой задачи между различными проектами, которые будут соответствовать

определённым кристаллам ПЛИС многокристальной РВС и учитывать топологию связей

между кристаллами ПЛИС. Учет особенностей внутренней архитектуры, топологии и

элементной базы РВС существенно усложняет специалисту-схемотехнику разработку

конфигураций вычислительной системы прикладной задачи для многокристальных РВС

и практически исключает возможность переноса (портации) готового решения на РВС

другой конфигурации или архитектуры. Программирование РВС осуществляется в два

этапа: на первом этапе схемотехник создает вычислительную структуру для решения

прикладной задачи, а на втором этапе прикладной программист создает

параллельную программу, определяющую потоки данных в созданной схемотехником

вычислительной структуре. Поэтому сроки разработки решения прикладной задачи

для РВС достаточно велики и составляют 4-9 месяцев.

Отличительными особенностями

комплекса программного обеспечения на основе языка программирования COLAMO по сравнению с известными средствами разработки MitrionC [12] и CatapultC [13],

являются автоматическое размещение, синхронизация и создание конфигурации для

многокристальных РВС, высокий процент заполнения кристалла (60-90%) и высокие

частоты работы (250 – 350 МГц).

Наиболее характерной

отличительной особенностью комплекса программного обеспечения РВС является

поддержка проблемно-ориентированных софт-архитектур, позволяющих создавать и

программировать макрообъекты, представляющие собой совокупность вычислительных

устройств, выполняющих определенную группу команд и соединенных между собой

коммутационной системой. Макрообъект – это совокупность вычислительных

устройств, выполняющих определенную группу команд и соединенных между собой

коммутационной системой. Для каждого класса задач, решаемых на РВС, можно

подобрать определенный набор оптимальных вычислительных структур (макрообъектов),

наиболее эффективно решающие задачи данного класса. Для макрообъекта допустимо

изменение количества функциональных вычислительных устройств и их параметров

(разрядности операндов, числа информационных каналов, системы команд и т.п.),

но недопустимо изменение их назначения. Таким образом, макрообъект с точки

зрения прикладного программиста является «заготовкой», которая может

доопределяться им при создании конкретного технического решения, а затем

тиражироваться в нужном количестве в ПЛИС вычислительных модулей и соединяться

с подобными или другими макрообъектами в вычислительные структуры, которые

оптимально соответствуют структуре решаемой задачи. На основе макрообъектов

возможно создание «софт-архитектуры РВС», под которой понимается созданная

схемотехником вычислительная структура, содержащая макрообъекты, в которой

можно без перезагрузки файлов конфигурации ПЛИС вычислительного поля с помощью

программной настройки изменять коммутацию между устройствами и создавать

необходимые вычислительные структуры для решения прикладных задач пользователя.

Это обеспечивает при

сохранении преемственности принципов программирования и использования языка

высокого уровня для программирования РВС возможность простой адаптации

программных компонентов средств разработки для РВС при переходе на новые

топологии ПВМ без внесения существенных изменений в код программных компонентов

комплекса, а также позволяет сократить время решения прикладных задач.

Для создания софт-архитектур

разработан язык SADL (Soft-Architecture Development Language) [14], который транслируется в виртуальную

архитектуру вычислительной системы для синтезатора Fire!Constructor, на

которую отображается информационный граф прикладной задачи. Для создания

софт-архитектуры выполняются:

- разработка описания софт-архитектуры

на языке SADL;

- трансляция описания

софт-архитектуры в промежуточное представление при помощи синтезатора

конфигураций параллельно-конвейерных вычислительных структур Fire!Constructor;

- размещение элементов

софт-архитектуры на аппаратной платформе при помощи синтезатора масштабируемых

параллельно-конвейерных процедур Steam!Constructor.

Транслятор языка SADL

преобразует текст программы в промежуточное представление, используемое

синтезатором FireConstructor для размещения на

аппаратной платформе РВС. Результатом размещения софт-архитектуры на аппаратную

платформу являются модифицированный файл промежуточного представления и

конфигурационные файлы для ПЛИС, участвующих в размещении софт-архитектуры на

аппаратной платформе РВС. После того как софт-архитектура была размещена на

аппаратной платформе РВС, она может быть использована для решения различных

прикладных задач заданной проблемной области.

Основными этапами разработки

прикладной программы для софт-архитектуры РВС являются:

- разработка параллельной

программы на языке высокого уровня COLAMO;

- трансляция параллельной

программы, преобразование информационного графа в структурный и процедурный

компоненты;

- отображение

структурного компонента параллельной программы на софт-архитектуру при помощи

синтезатора конфигураций параллельно-конвейерных вычислительных структур SteamConstructor;

- трансляция процедурного

компонента параллельной программы на уровень команд устройств софт-архитектуры;

- формирование

загрузочного out-файла, содержащего команды элементов софт-архитектуры;

- загрузка

конфигурационных файлов ПЛИС, полученных в результате размещения элементов

софт-архитектуры на аппаратной платформе реконфигурируемой системы;

- загрузка out-файла;

- загрузка в

софт-архитектуру исходных данных решаемой задачи;

- запуск программы на

исполнение и выгрузку результатов.

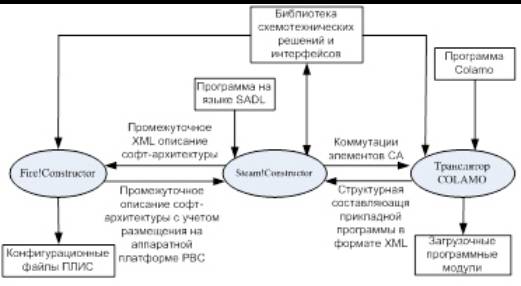

Взаимодействие средств

разработки прикладных программ при разработке софт-архитектуры показано

на рис. 2.

Рис. 2. Взаимодействие средств разработки прикладных программ

Благодаря разработанным

программным средствам разработка и модификация софт-архитектур не требуют

привлечения высококвалифицированного специалиста-схемотехника для изменения

вычислительной структуры. При этом время, затрачиваемое на создание или

модификацию софт-архитектуры, значительно сокращается, а получаемые

многокристальные архитектурные решения сравнимы по эффективности с решениями,

выполненными специалистами-схемотехниками вручную. В соответствии с основными

принципами языка COLAMO параллельные прикладные

программы могут быть легко модифицированы для адаптации к доступному

вычислительному ресурсу. Автоматизация отображения графов на ресурс РВС позволяет

разработчикам прикладных задач мыслить не несколькими ПЛИС, а одной виртуальной

ПЛИС с большим логическим объёмом. Комплекс разработанных программных средств

позволяет программисту РВС разрабатывать и выполнять отладку прикладных

параллельных программ для РВС, не вникая в особенности архитектуры РВС, а также

самостоятельно создавать и модифицировать различные софт-архитектуры,

ориентируясь на предметную область, которой принадлежит решаемая задача.

Литература:

1. Каляев

А.В., Левин И.И. Модульно-наращиваемые многопроцессорные системы со

структурно-процедурной организацией вычислений. М.: Янус-К, 2003. 380 с.

2. http://www.nallatech.com/(дата обращения 23.02.2015)

3. http://picocomputing.com/(дата обращения 23.02.2015)

4. http://www.conveycomputer.com/(дата обращения 23.02.2015)

5. http://www.maxeler.com/(дата обращения 23.02.2015)

6. http://www.srccomp.com/(дата обращения 23.02.2015)

7. Каляев И.А., Левин

И.И., Семерников Е.А., Шмойлов В.И. Реконфигурируемые мультиконвейерные

вычислительные структуры /Изд. 2-е, перераб. и доп. / Под общ. ред. И.А.

Каляева. Ростов-на-Дону: Изд-во ЮНЦ РАН, 2009. 344 с.

8. Каляев И.А., Левин

И.И. Семейство реконфигурируемых вычислительных системы с высокой реальной

производительностью // Труды международной научной конференции «Параллельные

вычислительные технологии» (ПАВТ’2009). Нижний Новгород: электронное издание

НГУ имени Н.И. Лобачевского, 2009. С.186-196.

9. Дордопуло А.И., Каляев

И.А., Левин И.И., Семерников Е.А. Высокопроизводительные реконфигурируемые

вычислительные системы нового поколения // Труды Международной

суперкомпьютерной конференции с элементами научной школы для молодежи «Научный

сервис в сети Интернет: экзафлопсное будущее». М.: Изд-во МГУ, 2011. С. 42-49.

10. Каляев И.А., Левин

И.И., Семерников Е.А., Дордопуло А.И. Реконфигурируемые вычислительные системы

на основе ПЛИС семейства Virtex-6 //

Сборник трудов Международной научной конференции «Параллельные вычислительные

технологии 2011» (ПАВТ 2011). Челябинск-М.: Издательский центр ЮУрГУ

[Электронный ресурс], 2011. С. 203–210.

11. I.A. Kalyaev, I.I. Levin, E.A. Semernikov, V.I. Shmoilov.

(2012). Reconfigurable multipipeline computing structures. Nova Science

Publishers, New York.

______________________________________

*Работа выполнена при финансовой поддержке Министерства образования и науки РФ по Соглашению о предоставлении субсидии №14.578.21.0006 от 05.06.2014, уникальный идентификатор RFMEFI57814X0006, гранту Южного федерального университета №213.01-2014/014 и НИР №2257 базовой части государственного задания №2014/174.